Circuits for Signal Processing in Communication Systems

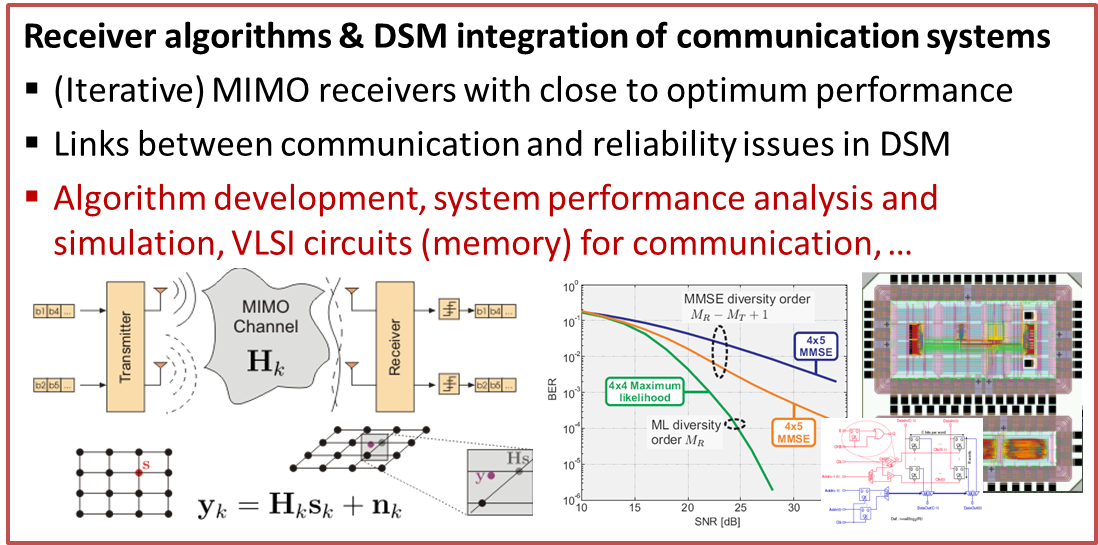

State-of-the-art wireless and wireline communication systems rely on highly complex digital signal processing algorithms to maximize spectral efficiency and to mitigate the impairments of the wireless and wireline channel. Reducing the computational complexity of these algorithms and devising hardware-efficient low-power architectures for their implementation is the main goal of our research.

Specific research interests include

- Algorithms and circuits for advanced MIMO detection

- Iterative receivers

- Dedicated and application-specific processor architectures (using the CoWare Processor Designer) for channel matrix preprocessing in MIMO communication

- Algorithms and architectures for lattice reduction

Circuits for Channel Coding

Channel coding is an integral part of virtually all wireless and wireline communication systems and circuits for decoding channel codes are almost always among the most difficult parts to implement efficiently (i.e., with low area and low power consumption) in hardware. In our research we focus on the hardware efficient, low-power implementation of channel decoding algorithms for digital communication.

Specific research interests include

- Low power turbo decoding

- Low power LDPC decoding (for 802.11n and 802.16e)

- Efficient hardware architectures and VLSI circuits for reducing area and power consumption of storage required for channel decoding

- VLSI Circuits for channel decoding with a throughput of multiple Gbps